Izgleda kako se pojavio novi problem nakon ekstremnog skoka u performansama zadnjih nekoliko generacija procesora. Tajna je u hranjenju procesora sa dovoljno podataka kako bi sve teklo bez čekanja. Taj zadatak obavlja cache memorija koja se u više razina nalazi direktno na samom silikonu procesora, a radi na principu pogađanja onoga što će procesoru trebati slijedeće. Uspješan pogodak osigurava vrlo brz rad, dok promašaj zahtjeva vađenje podatka sa spore DDR memorije i naravno prazan hod kod procesora.

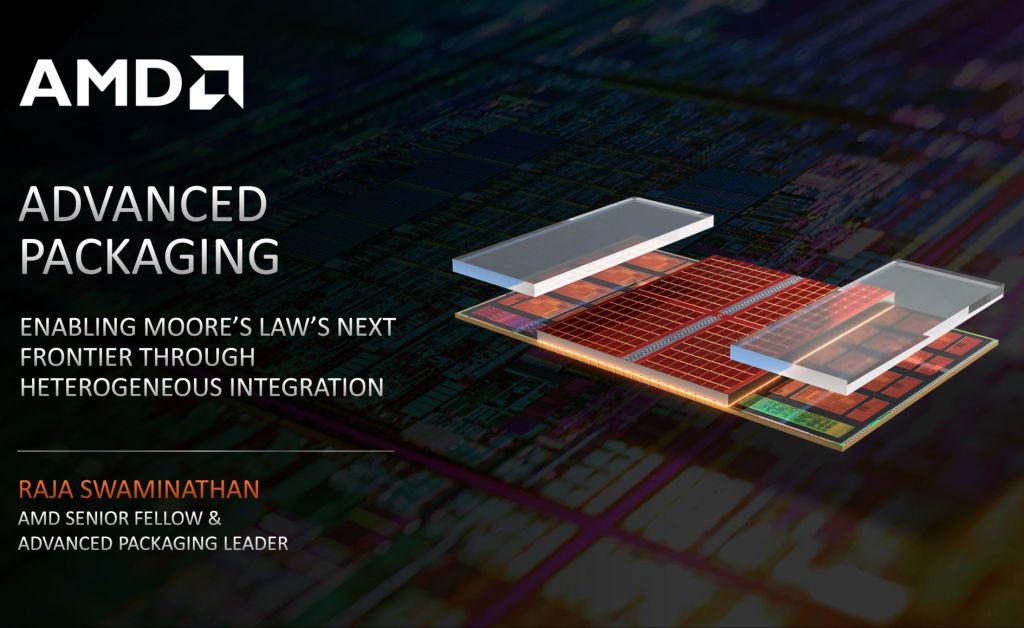

Osiguravanje većeg broja pogođenih podataka može se riješiti povećavanjem količine cache memorije, no ona sa svega 16 MiB zauzima prostora na čipu procesora koliko i 8 ZEN 3 jezgri. AMD tako planira stackati cache memoriju na ostale čipove implementacijom 3D V-Cache tehnologije. Time se otvara prostor za puno više cache memorije sa minimalnim udarcem na energiju i veličinu procesora, a potencijalno objašnjava i fizički deblji heatspreader na nadolazećim AM5 arhitekturama.

AMD je najavio stackanje i drugih komponenti jedne na drugu, što uključuje i same čiplete sa jezgrama, no sve će ovisiti i o snazi samih procesora, njihovoj potrošnji energije (zagrijavanju) kao i samoj ciljanoj cijeni koju procesori trebaju zadovoljiti.

Ove tehnologije razvijene su zajedno sa TSMC-om kod kojih se čipovi i tiskaju. Tehnologija radi zahvaljujući Micro Bump 3D implementaciji koja vertikalno povezuje čipove bakrenim vodovima.